CXCL3471BC8系列是能在低频输入8kHz, 4095倍的范围内倍频工作的PLL时钟发生器IC。小型化, 同步抖动小, 实现128倍, 256倍, 512倍等高倍频。分频电路, 相位频率比较器, 电荷泵, VCO内置,不需要复杂的滤波因子的计算, ,只需要加上电源和输入时钟就可简单实现时钟变换。另外,可用于和音频DAC的LR时钟相位同步的噪声修整用的主时钟的生成等,也适用于生成各种必须和输入信号同步的同步信号。输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。从CE端子输入低电平信号,可停止整个芯片动作,抑制消耗电流,此时的输出状态为高阻抗。可以选择SOT-26W和USP-6C封装。此外,本产品的输入端分频因子(M), 输出端分频因子(N), 以及电压泵电流(Ip)的设定值,均可按客户要求时提供部分的客户定制品。有需要时请提供详细的规格要求(输入输出频率,工作电源电压),并提前向本公司的各分公司询问对应的可能性。

[ CXCL3471BC8 ]

产品技术资料帮助

查看全部>

7.相关产品

产品概述 返回TOP

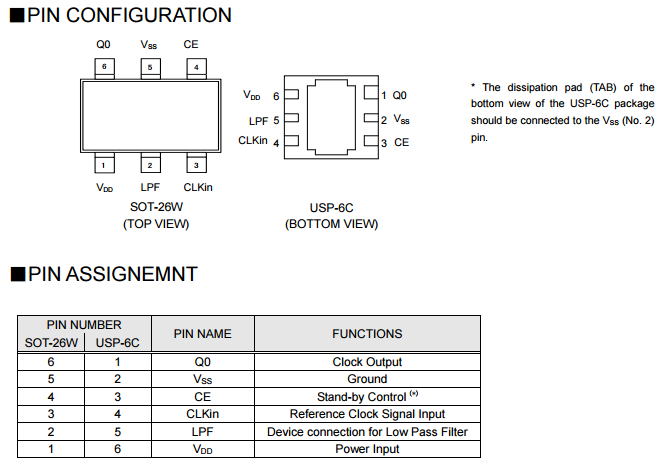

CXCL3471BC8系列是能在低频输入8kHz, 4095倍的范围内倍频工作的PLL时钟发生器IC。小型化, 同步抖动小, 实现128倍, 256倍, 512倍等高倍频。分频电路, 相位频率比较器, 电荷泵, VCO内置,不需要复杂的滤波因子的计算, ,只需要加上电源和输入时钟就可简单实现时钟变换。另外,可用于和音频DAC的LR时钟相位同步的噪声修整用的主时钟的生成等,也适用于生成各种必须和输入信号同步的同步信号。输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。从CE端子输入低电平信号,可停止整个芯片动作,抑制消耗电流,此时的输出状态为高阻抗。可以选择SOT-26W和USP-6C封装。此外,本产品的输入端分频因子(M), 输出端分频因子(N), 以及电压泵电流(Ip)的设定值,均可按客户要求时提供部分的客户定制品。有需要时请提供详细的规格要求(输入输出频率,工作电源电压),并提前向本公司的各分公司询问对应的可能性。The CXCL3471BC8 series is an ultra small PLL clock generator IC which can generate a high multiplier output up to 4095 from an input frequency as low as 8kHz. The series includes a divider circuit, phase/frequency comparator, charge pump, and VCO so it is possible to configure a fully operational circuit with a few external components like one low-pass filter capacitor. The Input divider ratio (M) can be selected from a range of 1 to 2047, the output divider ratio (N) can be selected from a range of 1 to 4095 and they are set internally by using laser timing technologies. Output frequency (fQ0) is equal to input clock frequency (fCLKin) multiplied by N/M. Output frequency range is 1MHz to 100MHz. Reference clock from 8kHz to 36MHz can be input as the input clock. The IC stops operation and current drain is suppressed when a low level signal is input to the CE pin which greatly reduces current consumption and produces a high impedance output. The setting of the input divider ratio (M), output divider ratio (N), and charge pump current (Ip) are factory fixed semi-custom. Please advise your Torex sales representative of your particular input/output frequency and supply voltage specifications so that we can see if we will be able to support your requirements. The series is available in small SOT-26W and USP-6C.

产品特点 返回TOP

应用范围 返回TOP

● Clock for controlling a Imaging dot (LCD)

● DSC (Digital still camera)

● DVC (Digital video camera)

● PND (Car navigation system)

● UMPC (Ultra Mobile Personal Computer)

● SSD (Solid State Disk)

● Digital Photo Frame

● Microcomputer and HDD drives

● Cordless phones & Wireless communication equipment

● Various system clocks

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

产品封装图 返回TOP

电路原理图 返回TOP

|

LL时钟发生器 |

|||||||

|

产品名称 |

特点 |

封装 |

电压范围(V) |

输出频率(MHz) |

消耗电流 (mA) |

||

|

MIN |

MAX |

MIN |

MAX |

||||

|

内置基频晶振电路PLL,对应高频 |

SOT-26 |

3 |

5 |

50 |

160 |

10 |

|

|

分頻因子:1.3~2047分頻倍 頻因子:6~2047倍頻 |

SOT-26 USP-6B |

2.97 |

5.5 |

3 |

30 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-25 USP-6C |

2.5 |

5.5 |

1 |

100 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-26W USP-6C |

2.5 |

5.5 |

1 |

100 |

5 |

|

◀ 上一篇:CXCL3471BC7输入端分频比M输出端分频比N的值均在1~256范围内通过激光微调方式自由选择输出时钟(fQ0)的频率等于标准时钟输入频率乘以N/M的比值(即fQ0=fCLKin×N/M)

下一篇▶:返回列表

|

|||||||||||||||||