7.相关产品

产品概述 返回TOP

产品特点 返回TOP

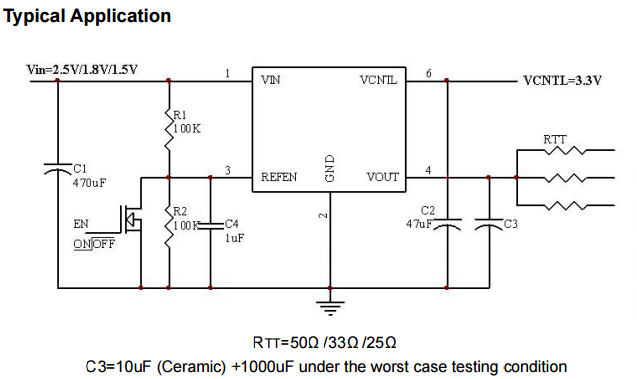

Ideal for DDR-I, DDR-II and DDR-III VTT Applications

Sink and Source 2A Continuous Current

Integrated Power MOSFETs

Generates Termination Voltage for SSTL_2, SSTL _18, HSTL, SCSI-2 and SCSI-3 Interfaces.

High Accuracy Output Voltage at Full-Load

Output Voltage traces REFEN Pin Voltage.

Low External Component Count

Shutdown for Suspend to RAM (STR) Functionality with High-Impedance Output

Current Limiting Protection

Thermal Shutdown Protection

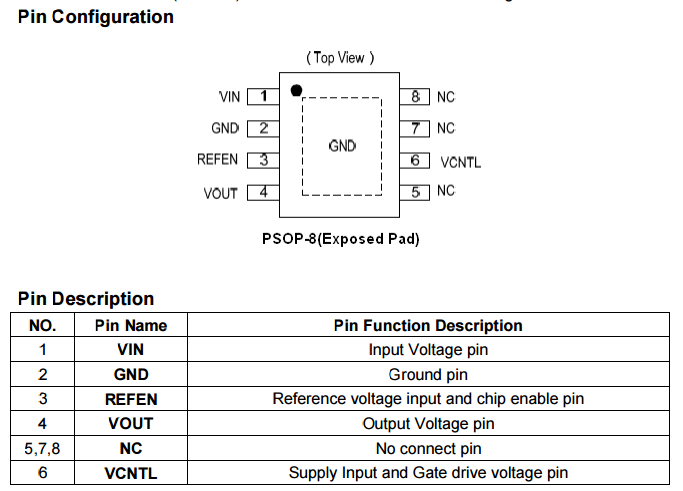

PSOP-8 with exposed pad Pb-Free Package.

应用范围 返回TOP

Desktop PCs, Notebooks, and Workstations

Graphics Card Memory Termination

Set Top Boxes, Digital TVs, Printers

Embedded Systems

Active Termination Buses

DDR-I, DDR-II and DDR-III Memory Systems

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

产品封装图 返回TOP

电路原理图 返回TOP

|

DDR Bus Termination Regulator(DDR总线终端稳压器) |

||||||

|

Product |

Status |

Output Offset Voltage |

Load Reg. |

Max Sink& Source Current |

VIN Max |

Control Voltage Range |

|

NRFND |

±20mV |

0.8%,1.2% |

3A |

6V |

3.3V to 6V |

|

|

Active |

±20mV |

0.50% |

1.5 |

6V |

3.3V to 6V |

|

|

Active |

±20mV |

0.50% |

2A |

6V |

3.3V to 6V |

|